# FM24C04A/08A 2-Wire Serial EEPROM

Data Sheet

Sep. 2009

INFORMATION IN THIS DOCUMENT IS INTENDED AS A REFERENCE TO ASSIST OUR CUSTOMERS IN THE SELECTION OF SHANGHAI FUDAN MICROELECTRONICS CO., LTD PRODUCT BEST SUITED TO THE CUSTOMER'S APPLICATION; THEY DO NOT CONVEY ANY LICENSE UNDER ANY INTELLECTUAL PROPERTY RIGHTS, OR ANY OTHER RIGHTS, BELONGING TO SHANGHAI FUDAN MICROELECTRONICS CO., LTD OR A THIRD PARTY. WHEN USING THE INFORMATION CONTAINED IN THIS DOCUMENTS, PLEASE BE SURE TO EVALUATE ALL INFORMATION AS A TOTAL SYSTEM BEFORE MAKING A FINAL DECISION ON THE APPLICABILITY OF THE INFORMATION AND PRODUCTS. SHANGHAI FUDAN MICROELECTRONICS CO., LTD ASSUMES NO RESPONSIBILITY FOR ANY DAMAGE, LIABILITY OR OTHER LOSS RESULTING FROM THE INFORMATION CONTAINED HEREIN. SHANGHAI FUDAN MICROELECTRONICS CO., LTD PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS. THE PRIOR WRITTEN APPROVAL OF SHANGHAI FUDAN MICROELECTRONICS CO., LTD IS NECESSARY TO REPRINT OR REPRODUCE IN WHOLE OR IN PART THESE DOCUMENTS.

Future routine revisions will occur when appropriate, without notice. Contact Shanghai Fudan Microelectronics Co., Ltd sales office to obtain the latest specifications and before placing your product order. Please also pay attention to information published by Shanghai Fudan Microelectronics Co., Ltd by various means, including Shanghai Fudan Microelectronics Co., Ltd home page (http://www.fmsh.com/).

Please contact Shanghai Fudan Microelectronics Co., Ltd local sales office for the specification regarding the information in this documents or Shanghai Fudan Microelectronics Co., Ltd products.

#### **Trademarks**

Shanghai Fudan Microelectronics Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Co., Ltd, Printed in the China, All Rights Reserved.

上海复旦微电子股份有限公司

Data Sheet

### **Description**

The FM24C04A/08A provides low operation voltage of 4096/8192 bits of serial electrically erasable and programmable read-only memory (EEPROM) organized as 512/1024 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operations are essential.

#### **Features**

- Low Operation Voltage: V<sub>CC</sub> = 1.7V to 5.5V

- 5V tolerant I/O

- Internally Organized: 512 x 8 (4K), 1024 x 8 (8K)

- 2-wire Serial Interface

- Schmitt Trigger, Filtered Inputs for Noise Suppression

- Bi-directional Data Transfer Protocol

- 1MHz (2.5V~5.5V) and 400 kHz (1.7V) Compatibility

- Write Protect Pin for Hardware Data Protection

- 16-byte Page Write Modes

- Partial Page Writes are Allowed

- Self-timed Write Cycle (5 ms max)

- High-reliability

- Endurance: 1,000,000 Write Cycles

- Data Retention: 100 Years

- PDIP8, SOP8, TSSOP8 Packages (RoHS Compliant and Halogen-free)

## **Absolute Maximum Ratings**

| Operating Temperature (Plastic Package)   | -55°C to +125°C |

|-------------------------------------------|-----------------|

| Operating Temperature (Module Package)    | -20°C to +60°C  |

| Storage Temperature (Plastic Package)     | -65°C to +150°C |

| Storage Temperature (Module Package)      | -25°C to +70°C  |

| Voltage on Any Pin with Respect to Ground | -1.0V to +7.0V  |

| Maximum Operating Voltage                 | 6.25V           |

| DC Output Current                         | 5.0 mA          |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

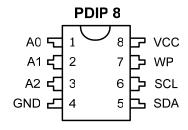

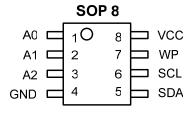

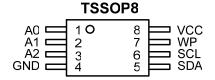

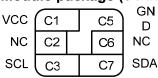

#### **Packaging Type**

# Module package (8 Pin) VCC C1 C5 GND NC C2 C6 NC SCL C3 C7 SDA

## **Pin Configurations**

| Pin Name        | Function                 |  |  |  |

|-----------------|--------------------------|--|--|--|

| A0~A2           | Device Address Inputs    |  |  |  |

| NC              | Not Connect              |  |  |  |

| SDA             | Serial Data Input/Output |  |  |  |

| SCL             | Serial Clock Input       |  |  |  |

| WP              | Write Protect            |  |  |  |

| V <sub>CC</sub> | Power Supply             |  |  |  |

| GND             | Ground                   |  |  |  |

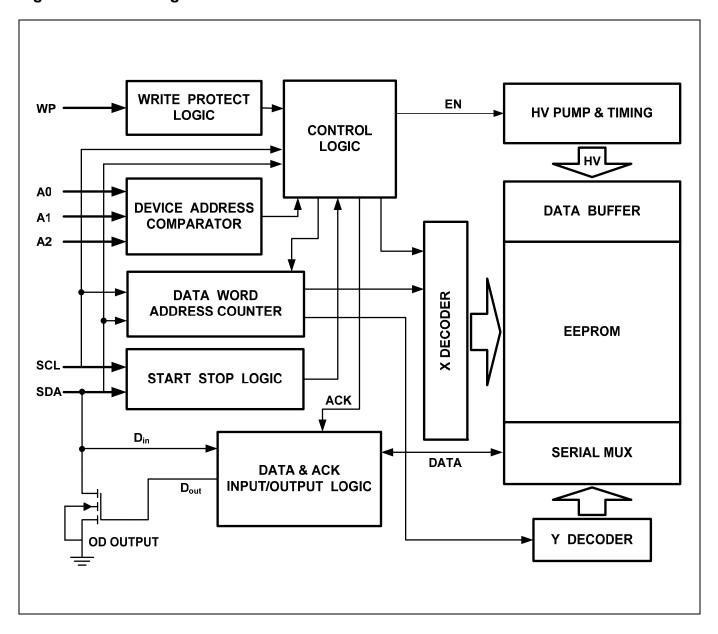

Figure 1. Block Diagram

#### **Pin Description**

**SERIAL CLOCK (SCL):** The SCL input is used to positive edge clock data into each EEPROM device and negative edge clock data out of each device.

**SERIAL DATA (SDA):** The SDA pin is bi-directional for serial data transfer. This pin is open-drain driven and may be wire-ORed with any number of other open-drain or open-collector devices.

**DEVICE/PAGE ADDRESSES (A2, A1):** The FM24C04A uses the A2 and A1 inputs for hard wire addressing and a total of four 4K devices may be addressed on a single bus system. The A0 pin is a no connect and can be connected to ground (device addressing is discussed in detail under the Device Addressing

section).

The FM24C08A only uses the A2 input for hardware addressing and a total of two 8K devices may be addressed on a single bus system. The A0 and A1 pins are no connects and can be connected to ground (device addressing is discussed in detail under the Device Addressing section).

WRITE PROTECT (WP): The FM24C04A/08A has a Write Protect pin that provides hardware data protection. The Write Protect pin allows normal read/write operations when connected to ground (GND). When the Write Protect pin is connected to  $V_{CC}$ , the write protection feature is enabled.

#### Write Protect Description

| WP Pin<br>Status   | Part of the Ar  | Part of the Array Protected     |  |  |  |  |  |

|--------------------|-----------------|---------------------------------|--|--|--|--|--|

|                    | FM 24C04A       | FM 24C04A FM 24C08A             |  |  |  |  |  |

| WP=V <sub>CC</sub> | Full (4K) Array | Full (4K) Array Full (8K) Array |  |  |  |  |  |

| WP=GND             | Normal Read/V   | Normal Read/Write Operations    |  |  |  |  |  |

## **Memory Organization**

**FM24C04A, 4K SERIAL EEPROM:** Internally organized with 32 pages of 16 bytes each, the 4K requires a 9-bit data word address for random word addressing.

**FM24C08A**, **8K SERIAL EEPROM**: Internally organized with 64 pages of 16 bytes each, the 8K requires a 10-bit data word address for random word addressing.

# Pin Capacitance

Applicable over recommended operating range from:  $T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = +1.7V$ .

| Symbol                       | Test Condition                                            | Max | Units | Conditions     |

|------------------------------|-----------------------------------------------------------|-----|-------|----------------|

| $C_{I/O}^{1}$                | Input/Output Capacitance (SDA)                            | 8   | pF    | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>1</sup> | Input Capacitance (A <sub>1</sub> , A <sub>2</sub> , SCL) | 6   | pF    | $V_{IN} = 0V$  |

Note: 1. This parameter is characterized and is not 100% tested.

#### **DC Characteristics**

Applicable over recommended operating range from:  $T_A = -40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  (Plastic Package) /  $T_A = -20^{\circ}\text{C} \sim +60^{\circ}\text{C}$  (Module Package), (unless otherwise noted).

| Symbol                       | Parameter              | Test Condition                          | Min                   | Тур  | Max                   | Units |

|------------------------------|------------------------|-----------------------------------------|-----------------------|------|-----------------------|-------|

| $V_{CC}$                     | Supply Voltage         |                                         | 1.7                   |      | 5.5                   | V     |

| I <sub>CC1</sub>             | Supply Current         | V <sub>CC</sub> = 5.5V, Read at 400K    |                       | 0.4  | 1.0                   | mA    |

| I <sub>CC2</sub>             | Supply Current         | V <sub>CC</sub> = 5.5V, Write at 400K   |                       | 2.0  | 3.0                   | mA    |

| I <sub>SB1</sub>             | Standby Current        | $V_{CC} = 1.7V, V_{IN} = V_{CC}/V_{SS}$ |                       | 3    | 6                     | μA    |

| I <sub>SB2</sub>             | Standby Current        | $V_{CC} = 5.5V, V_{IN} = V_{CC}/V_{SS}$ |                       | 8    | 18                    | μA    |

| I <sub>LI</sub>              | Input Leakage Current  | $V_{IN} = V_{CC}/V_{SS}$                |                       | 0.10 | 3.0                   | μA    |

| $I_{LO}$                     | Output Leakage Current | $V_{OUT} = V_{CC}/V_{SS}$               |                       | 0.05 | 3.0                   | μA    |

| V <sub>IL</sub> <sup>1</sup> | Input Low Level        |                                         | -0.6                  |      | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub> <sup>1</sup> | Input High Level       |                                         | V <sub>CC</sub> x 0.7 |      | 5.5                   | V     |

| $V_{OL2}$                    | Output Low Level       | $V_{CC}$ = 3.0V, $I_{OL}$ = 2.1 mA      |                       |      | 0.4                   | V     |

| $V_{OL1}$                    | Output Low Level       | $V_{CC}$ = 1.7V, $I_{OL}$ = 0.15 mA     |                       |      | 0.2                   | V     |

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

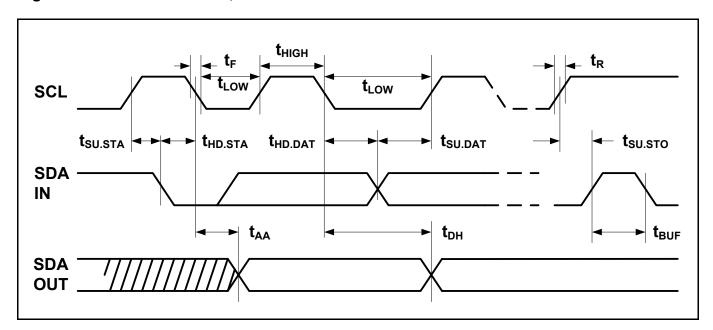

#### **AC Characteristics**

Applicable over recommended operating range from:  $T_A$  = -40°C ~ +85°C (Plastic Package) /  $T_A$  = -20°C ~ +60°C (Module Package) ,  $V_{CC}$  = +1.7V to +5.5V, CL = 1 TTL Gate and 100 pF (unless otherwise noted). Test conditions are listed in Note 2.

| Symbol              | Parameter                        | 1.7-volt  |     | 2.5-volt |                 | 5.5-volt |      | Units |

|---------------------|----------------------------------|-----------|-----|----------|-----------------|----------|------|-------|

| Syllibol            | r ai ailietei                    |           | Max | Min      | Max             | Min      | Max  | Units |

| f <sub>SCL</sub>    | Clock Frequency, SCL             |           | 400 |          | 1000            |          | 1000 | kHz   |

| $t_{LOW}$           | Clock Pulse Width Low            | 1.3       |     | 0.4      |                 | 0.4      |      | μs    |

| t <sub>HIGH</sub>   | Clock Pulse Width High           | 0.6       |     | 0.4      |                 | 0.4      |      | μs    |

| t <sub>AA</sub>     | Clock Low to Data Out Valid      | 0.1       | 0.9 | 0.05     | 0.55            | 0.05     | 0.55 | μs    |

| t <sub>BUF</sub> 1  | Time the bus must be free before |           |     | 0.5      |                 | 0.5      |      | μs    |

| t <sub>HD.STA</sub> | Start Hold Time                  | 0.6       |     | 0.25     |                 | 0.25     |      | μs    |

| t <sub>su.sta</sub> | Start Setup Time                 | 0.6       |     | 0.25     |                 | 0.25     |      | μs    |

| t <sub>HD.DAT</sub> | Data In Hold Time                | 0         |     | 0        |                 | 0        |      | μs    |

| t <sub>SU.DAT</sub> | Data In Setup Time               | 100 100   |     |          | 100             |          | ns   |       |

| t <sub>R</sub>      | Inputs Rise Time                 |           | 0.3 |          | 0.3             |          | 0.3  | μs    |

| t <sub>F</sub>      | Inputs Fall Time                 |           | 300 |          | 100             |          | 100  | ns    |

| t <sub>su.sto</sub> | Stop Setup Time                  | 0.6       |     | 0.25     |                 | 0.25     |      | μs    |

| t <sub>DH</sub>     | Data Out Hold Time               | 50        |     | 50       |                 | 50       |      | ns    |

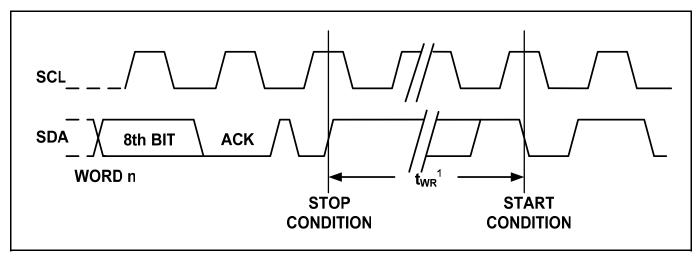

| t <sub>WR</sub>     | Write Cycle Time                 |           | 5   |          | 5               |          | 5    | ms    |

| Endurance 1         | 3.6V, 25°C, Page Mode            | 1,000,000 |     |          | Write<br>Cycles |          |      |       |

Notes: 1. This parameter is characterized and is not 100% tested.

2. AC measurement conditions:

RL (connects to  $V_{CC}$ ): 1.3 k $\Omega$  (2.5V, 5.5V), 10 k $\Omega$  (1.7V)

Input pulse voltages: 0.3  $V_{\text{CC}}$  to 0.7  $V_{\text{CC}}$

Input rise and fall times: ≤ 50 ns

Input and output timing reference voltages: 0.5 V<sub>CC</sub>

#### **Device Operation**

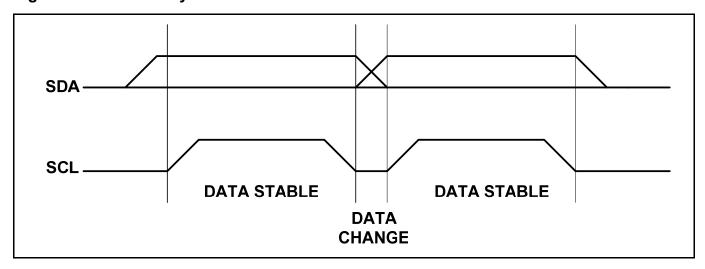

**CLOCK and DATA TRANSITIONS:** The SDA pin is normally pulled high with an external device. Data on the SDA pin may change only during SCL low time periods (refer to Figure 4). Data changes during SCL high periods will indicate a start or stop condition as defined below.

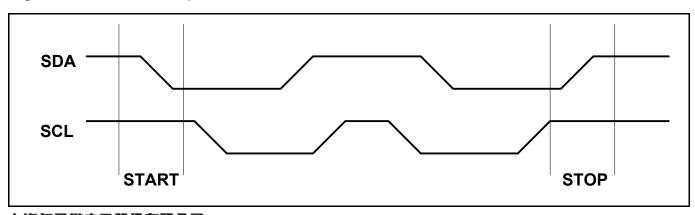

**START CONDITION:** A high-to-low transition of SDA with SCL high is a start condition which must precede any other command (refer to Figure 5).

**STOP CONDITION:** A low-to-high transition of SDA with SCL high is a stop condition. After a read sequence, the stop command will place the EEPROM in a standby power mode (refer to Figure 5).

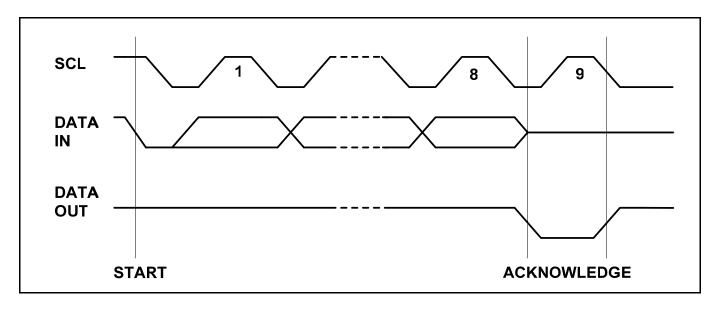

**ACKNOWLEDGE:** All addresses and data words are serially transmitted to and from the EEPROM in 8-bit words. The EEPROM sends a zero to acknowledge that it has received each word. This happens

during the ninth clock cycle. Following receipt each word from the EEPROM, the microcontroller should send a zero to EEPROM and continue to output the next data word or send a stop condition to finish the read cycle.

**STANDBY MODE**: The FM24C04A/08A features a low-power standby mode which is enabled: (a) upon power-up and (b) after the receipt of the stop bit and the completion of any internal operations.

**DEVICE RESET:** After an interruption in protocol, power loss or system reset, any 2-wire part can be reset in following these steps:

- 1. Clock up to 9 Cycles,

- 2. Look for SDA high in each cycle while SCL is high and then,

- 3. Create a start condition as SDA is high.

#### **Bus Timing**

Figure 2. SCL: Serial Clock, SDA: Serial Data I/O

# **Write Cycle Timing**

Figure 3. SCL: Serial Clock, SDA: Serial Data I/O

Note: 1. The write cycle time  $t_{WR}$  is the time from a valid stop condition of a write sequence to the end of the internal clear/write cycle.

Figure 4. Data Validity

Figure 5. Start and Stop Definition

上海复旦微电子股份有限公司

Data Sheet

Figure 6. Output Acknowledge

#### **Device Addressing**

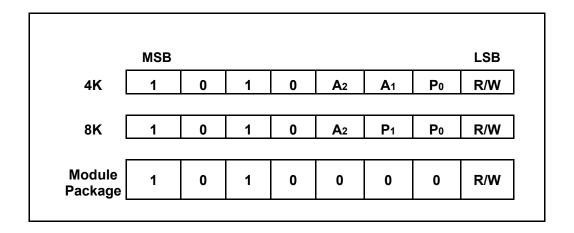

The 4K, 8K EEPROM device requires an 8-bit device address word following a start condition to enable the chip for a read or write operation (refer to Figure 7).

The device address word consists of a mandatory one, zero sequence for the first four most significant bits as shown. This is common to all the EEPROM devices.

The 4K EEPROM only uses the A2 and A1 device address bits with the third bit being a memory page address bit. The two device address bits must compare to their corresponding hard-wired input pins. The A0 pin is no connect.

The 8K EEPROM only uses the A2 device address bit with the next 2 bits being for memory page

addressing. The A2 must compare to its corresponding hard-wired input pin. The A1 and A0 pins are no connect.

The Module package device address word also consists of a mandatory one, zero sequence for the first four most significant bits. The next 3 bits are all zero.

The eighth bit of the device address is the read/write operation select bit. A read operation is initiated if this bit is high and a write operation is initiated if this bit is low.

Upon a compare of the device address, the EEPROM will output a zero. If a compare is not made, the chip will return to a standby state.

#### **Write Operations**

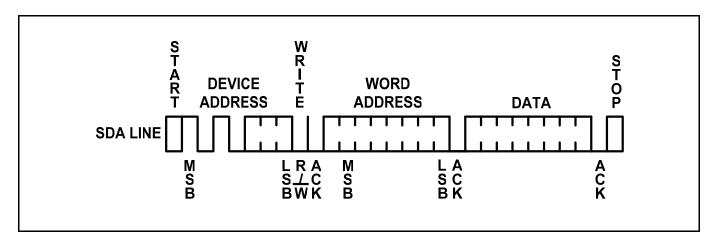

BYTE WRITE: A write operation requires an 8-bit data word address following the device address word and acknowledgment. Upon receipt of this address, the EEPROM will again respond with a zero and then clock in the first 8-bit data word. Following receipt of the 8-bit data word, the EEPROM will output a zero and the addressing device, such as a microcontroller, must terminate the write sequence with a stop condition. At this time the EEPROM enters an internally timed write cycle,  $t_{WR}$ , to the nonvolatile memory. All inputs are disabled during this write cycle and the EEPROM will not respond until the write is complete (refer to Figure 8).

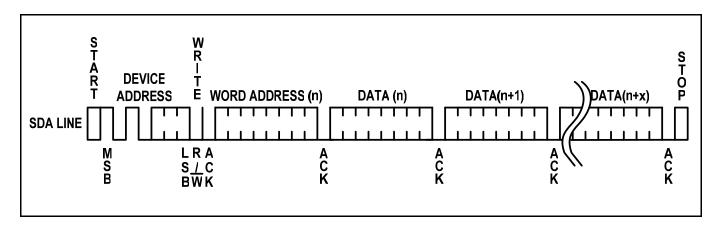

**PAGE WRITE:** The 4K, 8K devices are capable of 16-byte page writes.

A page write is initiated the same as a byte write, but the microcontroller does not send a stop condition after the first data word is clocked in. Instead, after the EEPROM acknowledges receipt of the first data word, the microcontroller can transmit up to fifteen more data words. The EEPROM will respond with a zero after each data word received. The microcontroller must terminate the page write sequence with a stop condition (refer to Figure 9).

The data word address lower four bits are internally incremented following the receipt of each data word. The higher data word address bits are not incremented, retaining the memory page row location. When the word address, internally generated, reaches the page boundary, the following byte is placed at the beginning of the same page. If more than sixteen data words are transmitted to the EEPROM, the data word address will "roll over" and previous data will be overwritten.

ACKNOWLEDGE POLLING: Once the internally timed write cycle has started and the EEPROM inputs are disabled, acknowledge polling can be initiated. This involves sending a start condition followed by the device address word. The read/write bit is representative of the operation desired. Only if the internal write cycle has completed will the EEPROM respond with a zero allowing the read or write sequence to continue.

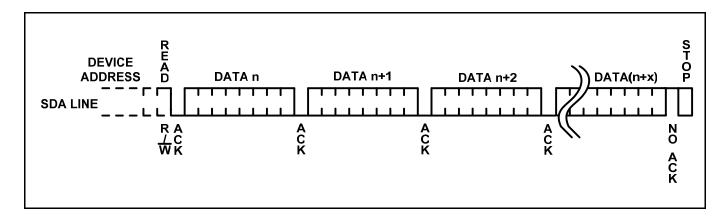

#### **Read Operations**

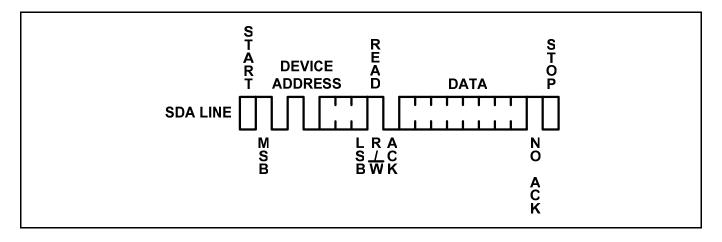

Read operations are initiated the same way as write operations with the exception that the read/write select bit in the device address word is set to one. There are three read operations: current address read, random address read and sequential read.

CURRENT ADDRESS READ: The internal data word address counter maintains the last address accessed during the last read or write operation, incremented by one. This address stays valid between operations as long as the chip power is maintained. The address "roll over" during read is from the last byte of the last memory page to the first byte of the first page. The address "roll over" during write is from the last byte of the current page to the first byte of the same page.

Once the device address with the read/write select bit set to one is clocked in and acknowledged by the EEPROM, the current address data word is serially clocked out. The microcontroller does not respond with an input zero but does generate a following stop condition (refer to Figure 10).

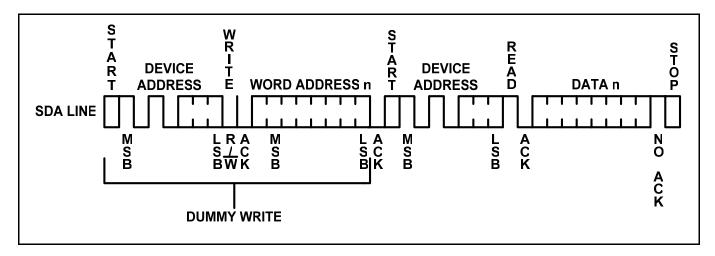

RANDOM READ: A random read requires a "dummy" byte write sequence to load in the data word address. Once the device address word and data word address are clocked in and acknowledged by the EEPROM, the microcontroller must generate another start condition. The microcontroller now initiates a current address read by sending a device address with the read/write select bit high. The EEPROM acknowledges the device address and serially clocks out the data word. The microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 11).

**SEQUENTIAL READ:** Sequential reads are initiated by either a current address read or a random address read. After the microcontroller receives a data word, it responds with an acknowledge. As long as the EEPROM receives an acknowledge, it will continue to increment the data word address and serially clock out sequential data words. When the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The sequential read operation is terminated when the microcontroller does not respond with a zero but does generate a following stop condition (refer to Figure 12)

Figure 7. Device Address

Figure 8. Byte Write

Figure 9. Page Write

Figure 10. Current Address Read

Figure 11. Random Read

Figure 12. Sequential Read

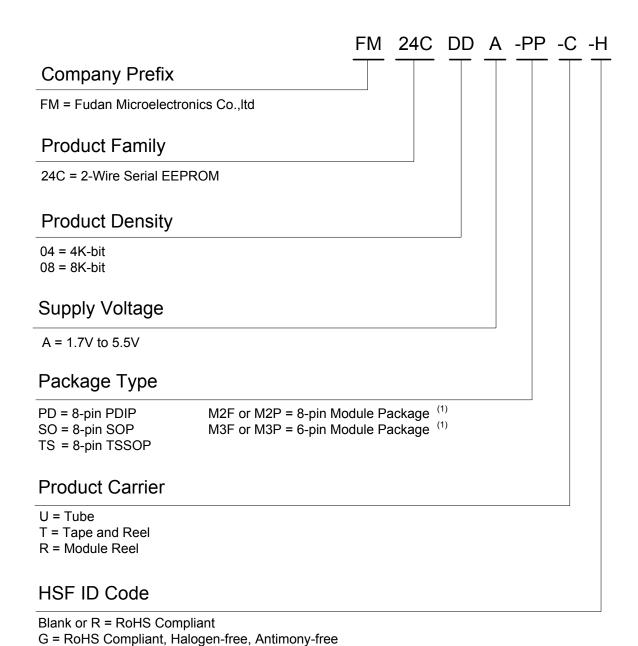

## **Ordering Information**

Note: 1. For the details of Module package please contact local sales office.

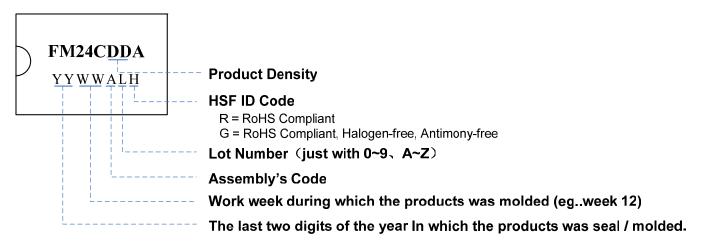

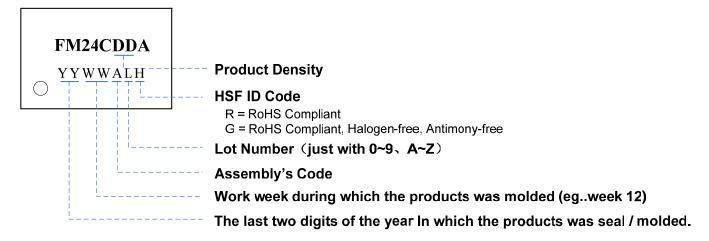

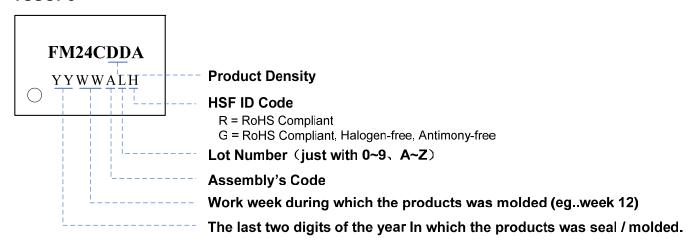

#### **Part Marking Scheme**

#### PDIP8

#### SOP8

#### TSSOP8

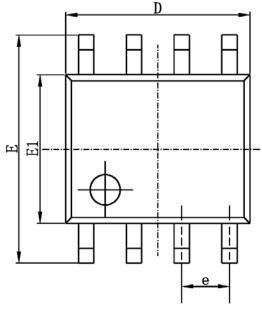

# **Packaging Information**

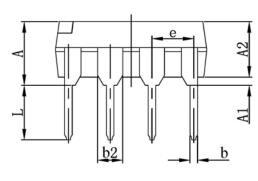

#### PDIP 8

| Symbol     | MIN        | MAX   |  |

|------------|------------|-------|--|

| Α          | 3.710      | 4.310 |  |

| <b>A</b> 1 | 0.510      |       |  |

| A2         | 3.200      | 3.600 |  |

| b          | 0.380      | 0.570 |  |

| b2         | 1.524(BSC) |       |  |

| С          | 0.204      | 0.360 |  |

| D          | 9.000      | 9.400 |  |

| E1         | 6.200      | 6.600 |  |

| E          | 7.320      | 7.920 |  |

| е          | 2.540(BSC) |       |  |

| L          | 3.000      | 3.600 |  |

| eB         | 8.400      | 9.000 |  |

#### NOTE:

1. Dimensions are in Millimeters.

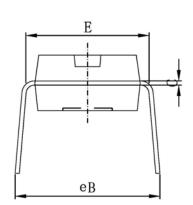

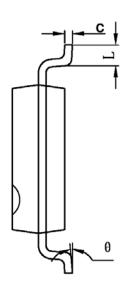

#### SOP 8

| Symbol | MIN        | MAX   |  |

|--------|------------|-------|--|

| Α      | 1.350      | 1.750 |  |

| A1     | 0.100      | 0.250 |  |

| A2     | 1.350      | 1.550 |  |

| b      | 0.330      | 0.510 |  |

| С      | 0.170      | 0.250 |  |

| D      | 4.700      | 5.100 |  |

| E1     | 3.800      | 4.000 |  |

| E      | 5.800      | 6.200 |  |

| е      | 1.270(BSC) |       |  |

| L      | 0.400      | 1.270 |  |

| θ      | 0°         | 8°    |  |

NOTE:

1. Dimensions are in Millimeters.

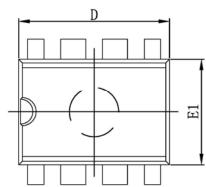

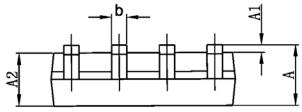

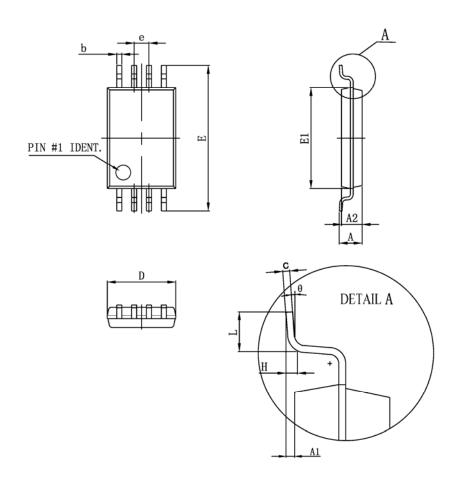

#### TSSOP8

| Symbol | MIN         | MAX   |  |

|--------|-------------|-------|--|

| D      | 2.900       | 3.100 |  |

| E1     | 4.300       | 4.500 |  |

| b      | 0.190       | 0.300 |  |

| С      | 0.090       | 0.200 |  |

| E      | 6.250       | 6.550 |  |

| Α      |             | 1.100 |  |

| A2     | 0.800       | 1.000 |  |

| A1     | 0.050       | 0.150 |  |

| е      | 0.650 (BSC) |       |  |

| L      | 0.500       | 0.700 |  |

| Н      | 0.250 (TYP) |       |  |

| θ      | 1°          | 7°    |  |

NOTE:

1. Dimensions are in Millimeters.

# **Revision History**

| Version | Publication date | Pages | Paragraph or Illustration                                          | Revise Description                                                                                                                                                                  |

|---------|------------------|-------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | Oct. 2008        | 20    |                                                                    | Preliminary                                                                                                                                                                         |

| 1.0     | Feb. 2009        | 20    | Feature Ordering Information Part Marking Scheme Sales and service | 1.Added the Information of Halogen-free     2.Updated the "Ordering Information"     3.Added the "Part Marking Scheme"     4.Updated the address and phone number of Beijing Office |

| 1.1     | Jun. 2009        | 20    | Packaging Type AC Characteristics Ordering Information             | <ol> <li>Added the 6-Pin Module package.</li> <li>Updated the AC characteristics.</li> </ol>                                                                                        |

| 1.2     | Sep. 2009        | 20    | Device Addressing<br>Packaging Information                         | <ul><li>1. Added the description of device addressing for Module package device.</li><li>2. Updated the packaging information.</li></ul>                                            |